**FP7-CLERECO** Grant Agreement FP7-611404

March 2016

## Microarchitecture Level Fault Injector for x86 Intel/AMD CPUs

#### **Product overview**

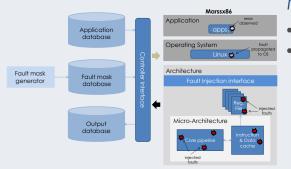

MaFIN is a complete microarchitecture level reliability evaluation framework for high performance computing systems. It is based on state-of-the-art statistical fault injection method or ACE analysis and built on MARSSx86 full-system simulator, providing accurate results for the entire CPU and all its components.

## Supported Architectures

$\Rightarrow$  Embedded and high performance x86-64 Intel and AMD architectures

### Extensions & Tools

- Caches extended with the data field (L1 data, L1 instruction and unified L2 cache)

- Prefetchers added for the first level caches

- Fully automated tools for:

- 1. running the golden run

- 2. fault mask generation

- fault injection in MARSSx86 3.

- Faults classification 4.

### Target Components

- Physical Register File (Int, FP)

- All fields of caches (L1 data and instruction, L2, L3)

- Prefetchers of L1 data, L1 instruction

- Load/Store Queue

- Load/Store Aliasing Table

- Issue Queue

- Branch Prediction Unit, RAS, BTBs

### Supported Fault Models

- Transient

- any multiple combina-

- Intermittent Permanent

- Measurements

- AVF/FIT, HVF

- Fault effect classification:

- Masked 1.

- 2. Silent Data Corruption (SDC)

- 3. Crash

- Assert 4.

- 5. Timeout

- 6. DUE

#### Flexible user extensible parser.

Measurements in any unmodified workload.

"Fast microarchitecture level framework for Intel/AMD x86-64 early reliability assessments"

- Computer Architecture Lab University of Athens

## **Speedup Features**

Speedup of fault injection campaigns is based on two runtime modes:

- Early Stop on Overwrite (ESO mode):

- $\Rightarrow$  No loss of accuracy

- $\Rightarrow$  Speedup:

- 2.6X for integer register file 1.5X for LSQ (data field) 2.9X for LSQ (address field) 1.4X for L1 data cache 1.5X for L1 instruction cache

- Early Stop on Overwrite or first Read (ESOR mode):

- $\Rightarrow$  Negligible loss of accuracy for structures in the core

- $\Rightarrow$  Speedup:

- 3.4X for integer register file 3.4X for LSQ (data field) 4.1X for LSQ (address field) 2.1X for L1 data cache

- 1.8X for L1 instruction cache

# nttps://twitter.com/CalDiUoa ര

#### Contact Us

University of Athens, Department of Informatics and Telecommunications Panepistimiopolis, Ilissia, GR 157 84, Athens, Greece (Office A32, 1st floor, Computer Architecture Lab)

> Dimitris Gizopoulos Phone: +30 210 727 5145, Fax: +30 210 727 5214 Email: dgizop AT di DOT uoa DOT gr

tion of model, compo-

nent, entry and cycle