Access and use of the content made available in the CLERECO institutional repository, at the website https://www.clereco.com/publications (the “Site”) or any successor repository based at CLERECO (the “Repository”), is based on your acceptance of these Terms of Use and applicable law, which you are deemed to accept and agree to by using the Site. If these Terms of Use are not accepted in full, you do not have permission to access the Repository and therefore should cease using this Site.

Copyright and other intellectual property rights subsist in the Site, in the works on deposit in the Repository (the “Works”) and in accompanying documentation and metadata.

Unless otherwise tagged or indicated with a different rights permission (e.g. a Work individually licensed by a specific Creative Commons Licence), Works may be re-used under the permitted act provisions of the Copyright, Designs and Patents Act 1988 (e.g. for a literary Work, a copy may be made under fair dealing for the purposes of private study and non-commercial research and brief extracts may be reproduced under fair dealing for the purpose of criticism or review of that Work or of another work). When using a Work please comply with the licence terms or permissions noted against the Work and cite or reference the title of the Work, its author/s, publication date and URL.

You may provide a hyperlink to the Site and individual Works without the prior consent of CLERECO, but such hyperlinks must display the relevant page or Work in the same form as the Site, without amendment or framing.

Metadata may be accessed free of charge and, except where otherwise specified, metadata may be re-used in any medium without prior permission for not-for-profit or non-commercial purposes provided the DOI identifier or a link to the original metadata record are given.

Access to some Works may be delayed because of publisher, research funder or internal embargo periods.

Unless stated otherwise, the Site and Works may contain advice, opinions, statements or other information by various authors or organisations. Reliance upon any such advice, opinion, statement or other information is at your risk and to the extent permitted by law CLERECO disclaims all liability and responsibility arising from any reliance placed on such information by your use of the Site or any Work or by anyone who may be informed of such information.

The Site and Works are provided on an “AS IS” and “AS AVAILABLE” basis and to the extent permitted by law the CLERECO excludes all warranties whether express or implied by law including but not limited to the warranties of merchantability and fitness for a particular purpose. CLERECO does not accept any liability arising from any inaccuracy or omission in the Site or any Work or otherwise on the Site or interruptions in the availability of the Site or any of its features or services.

In no event shall CLERECO be liable to any party for any of the following losses or damages (whether such losses be foreseen, foreseeable, known or otherwise): loss of data, loss of revenue or anticipated profits, loss of business, loss of opportunity, loss of goodwill or injury to reputation, loss suffered by third parties, any indirect, special, incidental, or consequential damages arising out of the use of the Site or any Work or services provided by the Site whether or not amended by third parties and regardless of form of action. This is not intended in any way to exclude or limit the liability of CLERECO for death or personal injury caused by its proven negligence or fraudulent misrepresentation.

Although the content of Works as deposited in the Repository is entirely the responsibility of respective author/s/depositor/s, if you are a rights holder and are concerned that you have found material on the Site for which you have not provided permission or is not covered by a statutory permitted act please contact the Repository with your contact details, a statement that you are the rights holder or are the authorised representative of the rights holder and the exact and full URL where you found the material.

The Site and Works may contain links to third party websites (“Linked Sites”). The Linked Sites are not owned or controlled by CLERECO and it is not responsible for the contents of any Linked Site. The inclusion of any link in the Site does not imply endorsement of any website or any association with its operators. You are responsible for viewing and abiding by the privacy, copyright and terms and conditions posted at the Linked Sites.

Nothing contained in the Site or in the provisions of services by the Repository shall be taken, construed or considered as a grant of any licence or right to use the trademarks displayed on the Site, which shall be deemed to include all logos, shields and service marks, including but not limited to those of CLERECO and of any third party displayed on the Site or in Work/s, without the prior written permission of their respective owner/s.

CLERECO reserves the right to vary these Terms of Use from time to time. Such variations become effective immediately upon the upload of the varied Terms of Use on the Site. By continuing to use the Site you will be deemed to accept such variations.

Nothing in these terms of use is intended to nor shall it confer any benefit on a third party whether under the Contracts (Rights of Third Parties) Act 1999 or otherwise. The failure or delay by CLERECO to exercise or enforce any right in these terms of use does not waive the right of CLERECO to enforce that right. If any of these terms of use should be determined to be illegal, invalid or otherwise unenforceable by reason of the laws of any country in which these terms of use are intended to be effective, then to the extent and within that jurisdiction in which that term of use is illegal, invalid or unenforceable, it shall be severed and deleted from these terms of use and the remaining terms of use shall survive and remain in full force and effect and continue to be binding and enforceable.

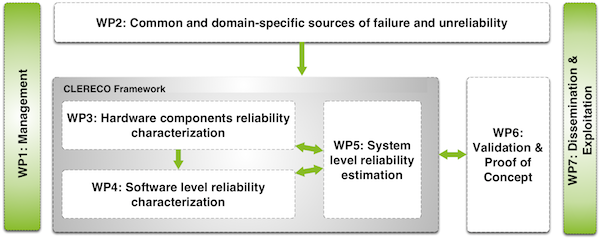

This WP includes all activities related for the appropriate coordination of both technical and administrative work between the CLERECO project partners and between them and the EC. Internal and external information flows will be defined, implemented and used as a result.

Leader: POLITO

Participants: UoA, CNRS, INTEL, THALES, YOGITECH, ABB

Dissemination of the CLERECO results to several selected groups of interested parties and exploitation of project results at the industrial and academic level is a key objective of the CLERECO project that will be pursued through the tasks of this WP. Given the importance of this activity a detailed dissemination plan and an exploitation strategy for the project will be developed and continuosly updated to reflect the results obtained from the research WPs.

Leader: INTEL

Participants: POLITO, UoA, CNRS, THALES, YOGITECH, ABB

WP6 is responsible for the validation of CLERECO early reliability estimation methodology and for the demonstration of project results exploiting deliverables and methods coming from WP3, WP4 and WP5.

Two main activities will be carried out within this WP. Although the main load of WP6 is at the end of the project, during the first half of the project it will define the evaluation methodology. The first activity will focus on the automation of all algorithms and methods defined within WP6 for the CLERECO reliability analysis within a prototype Electronic Design Automation (EDA) tool-suite. This is a mandatory task to enable the application of CLERECO methods to real test cases. The second activity will instead focus on the definition of realistic use-cases on which CLERECO concepts can be efficiently demonstrated and validated. This second activity will be steered by CLERECO industrial partners that will cooperate to the definition of relevant application examples.

Reliability of selected use cases will be analyzed through the developed EDA tool-suite at different design stages, considering different sets of available information, thus reproducing realistic situations typical of a product design cycle. Reliability results obtained through the use of the CLERECO method will be constantly compared to reliability measures obtained through traditional extensive (and clearly costly and time consuming) fault injection campaigns as well as laser/EM injections. This will enable CLERECO partners to clearly assess the accuracy of CLERECO estimation.

Eventually, CLERECO optimization design heuristics will be exploited to show how project results will help designers in optimizing developed systems gaining better performances.

Leader: THALES

Participants: POLITO, UoA, CNRS, INTEL, YOGITECH, ABB

WP5 contains the core activities of this project. Descriptions of the target systems and related parameters will be integrated into a comprehensive statistical model that will be used to estimate reliability metrics defined in WP2 (iteratively in the different design stages of the system). Together with reliability assessment, WP5 includes research on the development of algorithms to support designers with valuable instruments for reliability related decision-making process that will in turn allow the design of reliable systems with improved cost-related characteristics (area, energy/power, and performance) and reduced TTM.

The leading concepts that will be pursued are:

WP5 has also a key harmonization role of the research activity of this project. WP2, WP3, WP4 and WP5 are closely related WPs that require an intensive exchange of information to achieve their goals. Information must be properly represented and standardized in order to guarantee easy and reliable circulation and integration among tasks. WP5 is in charge of this through a dedicated task.

Finally, due to the complexity of the activities performed in this WP a constant validation of preliminary and intermediate results is mandatory. Research activities within WP5 will be therefore organized as a continue alternation of solutions development and preliminary validation activities on simple cases.

Leader: POLITO

Participants: UoA, CNRS, INTEL, THALES, YOGITECH, ABB

Similarly to WP3, WP4 iteratively breaks down the software stack into its basic components (from high-level application software modules down to the instruction set architecture level) that will be characterized form the reliability standpoint.

To enable early reliability estimations, software analysis must be possible at early system design stages, even when a target platform is not yet defined. To cope with this requirement, WP4 aims at defining metrics and models enabling to abstract the behavior of the software no matter the specific hardware architecture of the system.

Several activities will be addressed:

Once all these issues are covered, we will analyze each software component level: system, selected drivers and application. This analysis will be the foundation for the construction of a set of characterized software modules to be used in WP5 and WP6.

Finally, WP4 will also be engaged in the production of a preliminary library of characterized modules that will be exploited for the validation and demonstration activity of this project. Similar to WP3, realizing a full comprehensive library of components is out of the capacity of this project and we will only show the path for the analysis of future use cases.

Leader: CNRS

Participants: POLITO, UoA, INTEL, THALES, YOGITECH, ABB

In this WP hardware systems are iteratively broken down into their basic components that will be characterized form the reliability standpoint. With characterization here we intend the computation of specific parameters and measures potentially impacting the overall system reliability (e.g., area, error masking probability, resource utilization, timing constraints, etc.). This approach follows the concept of modular design/IP-reuse, for fast TTM that is a common challenge for both HPC and ES applications.

One of the key aspects of CLERECO is its cross-layer approach to reliability evaluation where all systems elements from the raw technologies up to the software layers are carefully considered with respect to their impact on system reliability. Hardware architectures will be analyzed considering their components (CPUs, memories, accelerators, peripherals, interconnects, etc.) at different levels of detail but always maintaining a connection between components and related user available instructions. The reliability-related behavior of hardware components at different stages of the system design cycle will be evaluated (in isolation): from very early specification stages, through high-level and more detailed design stages, down to the prototyping phases of the design flow. Thus, the reliability evaluation will be an iterative process providing different levels of detail while moving from the conceptual design phases, through all intermediate design phases, down to the post-silicon design validation phase.

Different sets of hardware components that will be studied are the following:

During the course of the project, different hardware components may emerge or may prevail in different market segments. The CLERECO research work is adaptable and flexible enough to consider the characteristics of new components even in later stages when the reliability evaluation framework has already been setup to some extent. Therefore, the impact of the emerging components in the overall system reliability will be normally considered.

For each hardware component, a set of important parameters for the reliability of the system will be extracted. In particular, the following important information will be either estimated or actually measured (depending on the level of abstraction of each phase of the design cycle):

Both ASIC and FPGA implementation of different cores will be analyzed in this WP to fully consider all design alternatives available when working on real computing systems.

Finally, WP3 will be also engaged in the implementation of a preliminary library of characterized modules that will be employed for the validation and demonstration activity of this project in WP6. It is worth to mention here that realizing a full comprehensive library of components is out of the capacity of this project. We will show here the path for the analysis of future use cases focusing on instruments that will allow a fast technology transfer from the research domain to real cases.

Leader: UoA

Participants: POLITO, CNRS, INTEL, THALES, YOGITECH, ABB

WP1 analyzes the different failure mechanisms that will be relevant in future technologies, which will be likely employed in the computing continuum (scaled bulk CMOS, III-V Ge, Finfets, spin logic, etc.) and works on identifying and characterizing the main sources of failure. Moreover, this WP also sets the reliability requirements for the different computing segments within the computing continuum such as ES and HPC.

The starting point of WP1 activities consists on studying the defects and reliability failure mechanisms that are anticipated in future computing systems (due to technology and architectural specifications). This operation involves the selection of a set of use cases ranging from very specific ES applications to general-purpose HPC systems. Among the wide range of possible use cases we will target those in which architectural and technological solutions among the ES and the HPC segments are rapidly converging including for instance multi/many cores in the 22/16nm Finfet technology node. Identified sources of failure will be characterized and will be used in the reliability estimation methodology developed in CLERECO.

System reliability is influenced by several parameters, which must all be carefully considered in the development of an accurate reliability evaluation framework. To take this into account, WP1 also aims at identifying the different operating modes of the system (e.g., voltage and frequency levels), and the different operating conditions (e.g., temperature, electronic noise, etc.).

The results of the project will be eventually captured in a series of reliability metrics that are required throughout heterogeneous segments of the computing continuum market. Some will be the well-known SDC/DUE FIT rates, but we expect to define some more metrics capturing different reliability aspects. Some will derive from safety standards, while some will derive from more implicit requirements (like the user experience, FIT rate that has impact on performance but not on correctness, etc.). WP1 is also in charge of determining the acceptable estimate error for the different design phases (from early abstract design phases up to final RTL).

WP Leader: INTEL

Participants: POLITO, UoA, CNRS, THALES, YOGITECH, ABB

What information do we collect?

We collect information from you when you register on our site.

When ordering or registering on our site, as appropriate, you may be asked to enter your: name or e-mail address. You may, however, visit our site anonymously.

What do we use your information for?

Any of the information we collect from you may be used in one of the following ways: To improve our website

(we continually strive to improve our website offerings based on the information and feedback we receive from you)

How do we protect your information?

We implement a variety of security measures to maintain the safety of your personal information when you enter, submit, or access your personal information.

Do we use cookies?

Yes (Cookies are small files that a site or its service provider transfers to your computers hard drive through your Web browser (if you allow) that enables the sites or service providers systems to recognize your browser and capture and remember certain information.

Do we disclose any information to outside parties?

We do not sell, trade, or otherwise transfer to outside parties your personally identifiable information. This does not include trusted third parties who assist us in operating our website, conducting our business, or servicing you, so long as those parties agree to keep this information confidential. We may also release your information when we believe release is appropriate to comply with the law, enforce our site policies, or protect ours or others rights, property, or safety. However, non-personally identifiable visitor information may be provided to other parties for marketing, advertising, or other uses.

Online Privacy Policy Only

This online privacy policy applies only to information collected through our website and not to information collected offline.

Your Consent

By using our site, you consent to our websites privacy policy.

Changes to our Privacy Policy

If we decide to change our privacy policy, we will update the Privacy Policy modification date below.

Advanced multifunctional computing systems realized in forthcoming technologies hold the promise of a significant increase of the computational capability that will offer end-users ever improving services and functionalities (e.g., next generation mobile devices, cloud services, etc.). However, the same path that is leading technologies toward these remarkable achievements is also making electronic devices increasingly unreliable posing a threat to our society that is depending on the computers and electronic devices in every aspect of human activities.

Reliability of electronic systems is therefore a key challenge for the whole information and communication technology and must be guaranteed without penalizing or slowing down the characteristics of the final products.

CLERECO research project recognizes early accurate reliability evaluation as one of the most important and challenging tasks toward this goal. Being able to precisely and early evaluate the reliability of a system means being able to carefully plan for specific countermeasures rather than resorting to worst-case approaches. CLERECO project will be fundamental in the development of scaled systems for more than a decade from present.

The proposed CLERECO framework for efficient reliability evaluation and therefore efficient exploitation of reliability oriented design approaches starting from early phases of the design process will enable circuit integration to continue at exponential rates and enable the design and manufacture of future systems for the computing continuum at a minimum cost (e.g., up to 50% less area, up to 50% less energy, etc.) contrary to existing worst-case-design solutions for reliability. The applications of such chips will play a major role in our society and can be seen through the prism of future computing systems ranging from avionics, automobile, smartphones, mobile systems, Personal Computers (PCs) and future servers utilized in the settings of Data Centers, Grid Computing, Cloud Computing and other types of HPC systems.

The project is structured into seve workpackages: 4 research workpackages, one workpackage for demonstration, one workpackage for dissemination and exploitation activities and finally one workpackage dedicated to management.